## The basics of logic design: Combinational logic

Yipeng Huang

**Rutgers University**

December 2, 2025

### Table of contents

Transistors: The building block of computers

### Combinational logic

Basic gates

More-than-2-input gates

#### Functional completeness

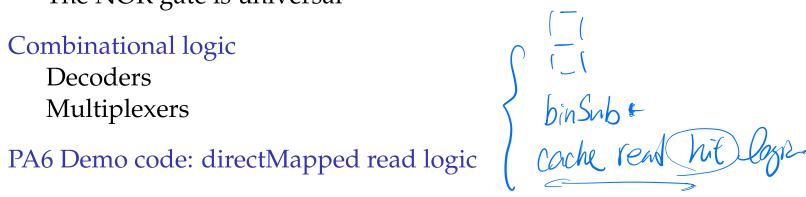

The set of logic gates {NOT, AND, OR} is universal The NAND gate is universal The NOR gate is universal

#### Combinational logic

Decoders Multiplexers

PA6 Demo code: directMapped read logic

## Computer organization

### Layer cake

- Society

- ► Human beings

- Applications

- Algorithms

- High-level programming languages

- Interpreters

- Low-level programming languages

- Compilers

- Architectures

- Microarchitectures

- Sequential/combinational logic

- Transistors

- Semiconductors

- Materials science

Combinational - s no state

1950 : Segrential - s Stateful.

## **Everything is bits**

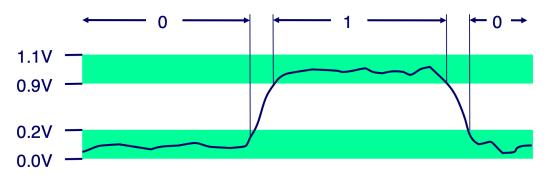

- Each bit is 0 or 1

- By encoding/interpreting sets of bits in various ways

- Computers determine what to do (instructions)

- ... and represent and manipulate numbers, sets, strings, etc...

- Why bits? Electronic Implementation

- Easy to store with bistable elements

- Reliably transmitted on noisy and inaccurate wires

## To build logic, we need switches

Vacuum tubes a.k.a. valves

Figure: Source: By Stefan Riepl (Quark48) - Self-photographed, CC BY-SA 2.0

https://commons.wikimedia.org/w/

index.php?curid=14682022

#### **Transistors**

- ► The first transistor. Developed at Bell Labs, Murray Hill, New Jeresy

- https://www.bell-labs.com/ about/locations/

**MOSFETs**

dicides. Bipolar Janution Inconsisters,

FZM.

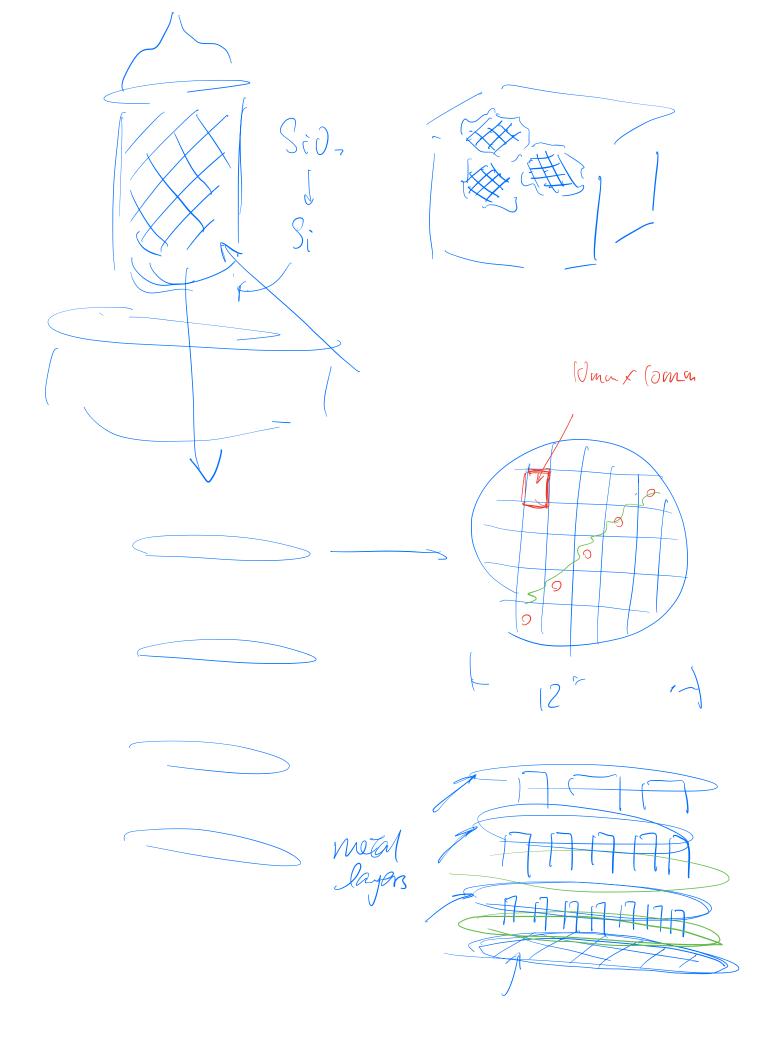

#### MOS: Metal-oxide-semiconductor

► A sandwich of conductor-insulator-semiconductor.

#### FET: Field-effect transistor

► Gate exerts electric field that changes conductivity of semiconductor.

B C N

## NMOS, PMOS, CMOS

Ga Ge. Ar

# PMOS: P-type MOS

- positive gate voltage, acts as open circuit (insulator)

- negative gate voltage, acts as short circuit (conductor)

## NMOS: N-type MOS

- positive gate voltage, acts as short circuit (conductor)

- negative gate voltage, acts as open circuit (insulator)

### CMOS: Complementary MOS

- A combination of NMOS and PMOS to build logical gates such as NOT, AND, OR.

- ▶ We'll go to slides posted in supplementary material to see how they work.

## Combinational vs. sequential logic

### Combinational logic

- No internal state nor memory

- Output depends entirely on input

- Examples: NOT, AND, NAND, OR, NOR, XOR, XNOR gates, decoders, multiplexers.

### Sequential logic

- Has internal state (memory)

- Output depends on the inputs and also internal state

- Examples: latches, flip-flops, Mealy and Moore machines, registers, pipelines, SRAMs.

### Table of contents

Transistors: The building block of computers

### Combinational logic

Basic gates More-than-2-input gates

#### Functional completeness

The set of logic gates {NOT, AND, OR} is universal The NAND gate is universal The NOR gate is universal

#### Combinational logic

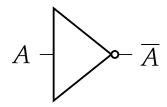

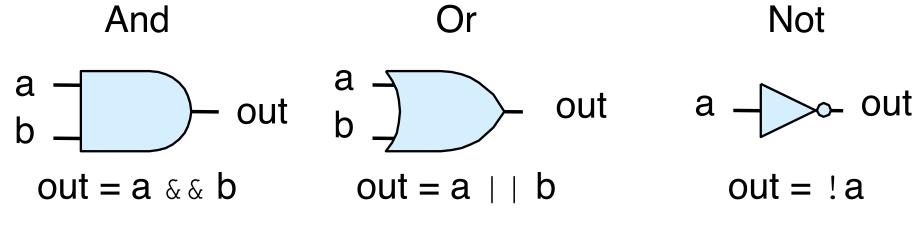

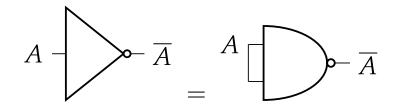

## NOT gate

| $\boldsymbol{A}$ | $\overline{A}$ |

|------------------|----------------|

| 0                | 1              |

| 1                | 0              |

Table: Truth table for NOT gate

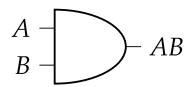

## AND gate, NAND gate

| $\boldsymbol{A}$ | В | AB |

|------------------|---|----|

| 0                | 0 | 0  |

| 0                | 1 | 0  |

| 1                | 0 | 0  |

| 1                | 1 | 1  |

Table: Truth table for AND gate

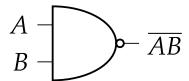

| $\boldsymbol{A}$ | В | $\overline{AB}$ |

|------------------|---|-----------------|

| 0                | 0 | 1               |

| 0                | 1 | 1               |

| 1                | 0 | 1               |

| 1                | 1 | 0               |

Table: Truth table for NAND gate

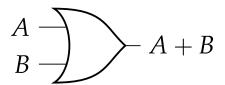

## OR gate, NOR gate

| $\boldsymbol{A}$ | В | A+B |

|------------------|---|-----|

| 0                | 0 | 0   |

| 0                | 1 | 1   |

| 1                | 0 | 1   |

| 1                | 1 | 1   |

Table: Truth table for OR gate

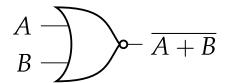

| $\boldsymbol{A}$ | В | $\overline{A+B}$ |

|------------------|---|------------------|

| 0                | 0 | 1                |

| 0                | 1 | 0                |

| 1                | 0 | 0                |

| 1                | 1 | 0                |

Table: Truth table for NOR gate

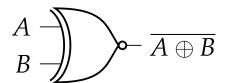

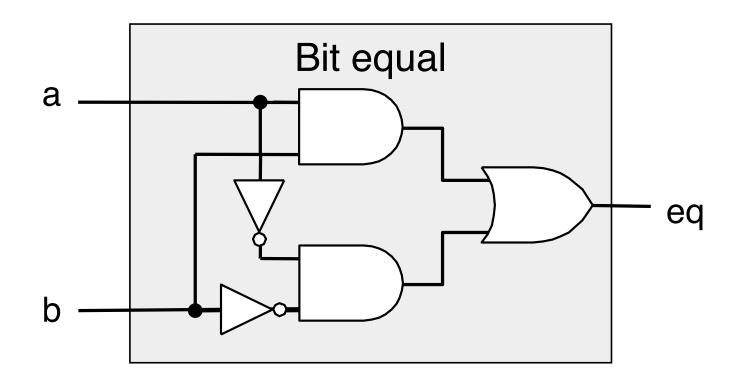

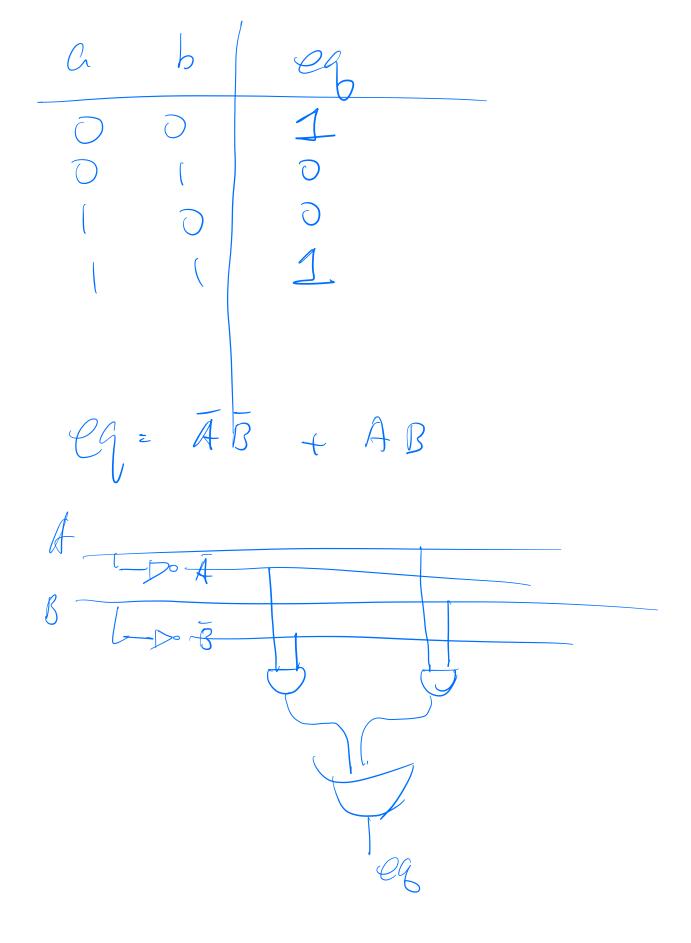

## XOR gate, XNOR gate

| $\boldsymbol{A}$ | В | $A \oplus B$ |

|------------------|---|--------------|

| 0                | 0 | 0            |

| 0                | 1 | 1            |

| 1                | 0 | 1            |

| 1                | 1 | 0            |

Table: Truth table for XOR gate

| $\boldsymbol{A}$ | В | $\overline{A \oplus B}$ |

|------------------|---|-------------------------|

| 0                | 0 | 1                       |

| 0                | 1 | 0                       |

| 1                | 0 | 0                       |

| 1                | 1 | 1                       |

Table: Truth table for XNOR gate

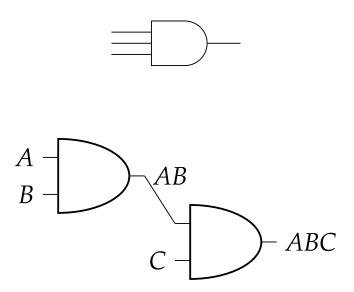

## More-than-2-input AND gate

| $\boldsymbol{A}$ | B | C | ABC |

|------------------|---|---|-----|

| 0                | 0 | 0 | 0   |

| 0                | 0 | 1 | 0   |

| 0                | 1 | 0 | 0   |

| 0                | 1 | 1 | 0   |

| 1                | 0 | 0 | 0   |

| 1                | 0 | 1 | 0   |

| 1                | 1 | 0 | 0   |

| 1                | 1 | 1 | 1   |

Table: Truth table for three-input AND gate

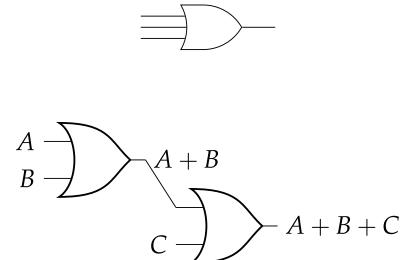

## More-than-2-input OR gate

| $\boldsymbol{A}$ | В | C | A+B+C |

|------------------|---|---|-------|

| 0                | 0 | 0 | 0     |

| 0                | 0 | 1 | 1     |

| 0                | 1 | 0 | 1     |

| 0                | 1 | 1 | 1     |

| 1                | 0 | 0 | 1     |

| 1                | 0 | 1 | 1     |

| 1                | 1 | 0 | 1     |

| 1                | 1 | 1 | 1     |

Table: Truth table for three-input OR gate

### Table of contents

Transistors: The building block of computers

### Combinational logic

Basic gates

More-than-2-input gates

#### Functional completeness

The set of logic gates {NOT, AND, OR} is universal The NAND gate is universal The NOR gate is universal

### Combinational logic

Decoders Multiplexers

PA6 Demo code: directMapped read logic

## The set of logic gates {NOT, AND, OR} is universal

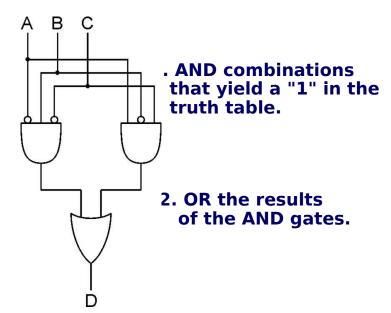

Or-of conds Sum-of-produces Figure: Source: CS:APP

## The set of logic gates {NOT, AND, OR} is universal

- Any truth table can be expressed as sum of products form.

- Write each row with output 1 as a product (minterm).

- Sum the products (minterm).

- Forms a disjunctive normal form (DNF).

- $D = \overline{A}B\overline{C} + A\overline{B}C$

- Always only needs NOT, AND, OR gates.

- Supplementary slides example...

### **Logical Completeness**

Can implement ANY truth table with AND, OR, NOT.

| A | В | С | D |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

Sum of products OR of AND clauses

## The set of logic gates {NOT, AND, OR} is universal

- Any truth table can be expressed as sum of products form.

- Write each row with output 1 as a product (minterm).

- Sum the products (minterm).

- Forms a disjunctive normal form (DNF).

- $D = \overline{A}B\overline{C} + A\overline{B}C$

- Always only needs NOT, AND, OR gates.

- Supplementary slides example...

Figure: Source: CS:APP

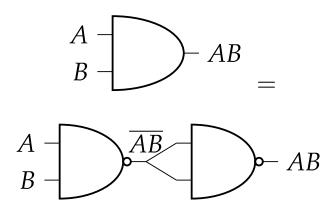

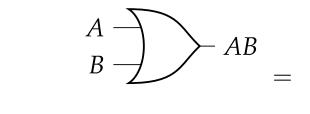

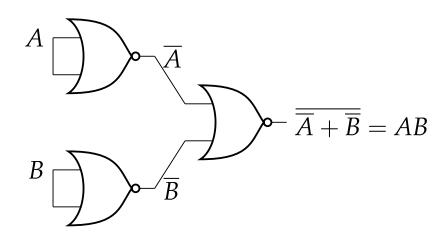

## The NAND gate is universal

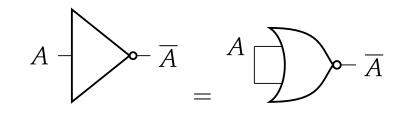

## NOT gate as a single NAND gate

| $\boldsymbol{A}$ | $\overline{A}$ | AA | $\overline{AA}$ |

|------------------|----------------|----|-----------------|

| 0                | 1              | 0  | 1               |

| 1                | 0              | 1  | 0               |

Table:  $\overline{A} = \overline{AA}$

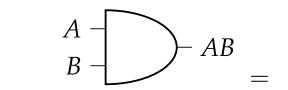

### AND gate as two NAND gates

| A | В | AB | $\overline{AB}$ | $\overline{\overline{AB}}$ |

|---|---|----|-----------------|----------------------------|

| 0 | 0 | 0  | 1               | 0                          |

| 0 | 1 | 0  | 1               | 0                          |

| 1 | 0 | 0  | 1               | 0                          |

| 1 | 1 | 1  | 0               | 1                          |

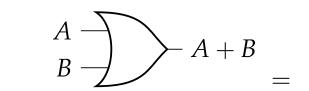

## The NAND gate is universal

### De Morgan's Law

| A | В | $\overline{A}$ | $\overline{B}$ | $\overline{A} \ \overline{B}$ | A+B                                                                                               | $\overline{A+B}$ |

|---|---|----------------|----------------|-------------------------------|---------------------------------------------------------------------------------------------------|------------------|

| 0 | 0 | 1              | 1              | 1                             | 0                                                                                                 | 1                |

| 0 | 1 | 1              | 0              | 0                             | 1                                                                                                 | 0                |

| 1 | 0 | 0              | 1              | 0                             | 1                                                                                                 | 0                |

| 1 | 1 | 0              | 0              | 0                             | $egin{array}{ c c c c } A + B & & & & \\ \hline 0 & & & & \\ 1 & & & & \\ 1 & & & & \\ 1 & & & &$ | 0                |

Table:  $\overline{A} \ \overline{B} = \overline{A + B}$

### OR gate as three NAND gates

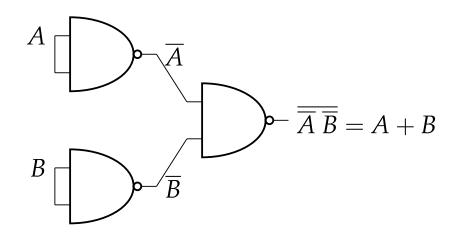

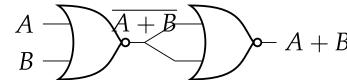

# The NOR gate is universal

## NOT gate as a single NOR gate

| $\boldsymbol{A}$ | $\overline{A}$ | A+A | $\overline{A+A}$ |

|------------------|----------------|-----|------------------|

| 0                | 1              | 0   | 1                |

| 1                | 1 0            | 1   | 0                |

Table:  $\overline{A} = \overline{A + A}$

## OR gate as two NOR gates

| A | В | A + B | A+B | $\overline{\overline{A+B}}$ |

|---|---|-------|-----|-----------------------------|

| 0 | 0 | 0     | 1   | 0                           |

| 0 | 1 |       | 0   | 1                           |

| 1 | 0 |       | 0   | 1                           |

| 1 | 1 | 1     | 0   | 1                           |

## The NOR gate is universal

### De Morgan's Law

| $\boldsymbol{A}$ | B | $\overline{A}$ | $\overline{B}$ | $\overline{A} + \overline{B}$ | AB | $\overline{AB}$ |

|------------------|---|----------------|----------------|-------------------------------|----|-----------------|

| 0                | 0 | 1              | 1              | 1                             | 0  |                 |

| 0                | 1 | 1              | 0              | 1                             | 0  | 1               |

| 1                | 0 | 0              | 1              | 1                             | 0  | 1               |

| 1                | 1 | 0              | 0              | 1<br>1<br>1<br>1<br>0         | 1  | 0               |

Table:  $\overline{A} + \overline{B} = \overline{AB}$

### AND gate as three NOR gates

## Combinational vs. sequential logic

### Combinational logic

- ► No internal state nor memory

- Output depends entirely on input

- Examples: NOT, AND, NAND, OR, NOR, XOR, XNOR gates, decoders, multiplexers.

### Sequential logic

- Has internal state (memory)

- Output depends on the inputs and also internal state

- Examples: latches, flip-flops, Mealy and Moore machines, registers, pipelines, SRAMs.

### Table of contents

Transistors: The building block of computers

### Combinational logic

Basic gates

More-than-2-input gates

#### Functional completeness

The set of logic gates {NOT, AND, OR} is universal The NAND gate is universal The NOR gate is universal

#### Combinational logic

Decoders Multiplexers

PA6 Demo code: directMapped read logic

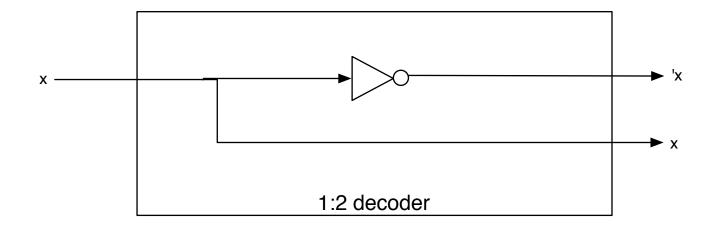

### **Decoders**

Takes n-bit input, uses it as an index to enable exactly one of  $2^n$  outputs

## Internal design of 1:2 decoder

Figure: Source: Mano & Kime

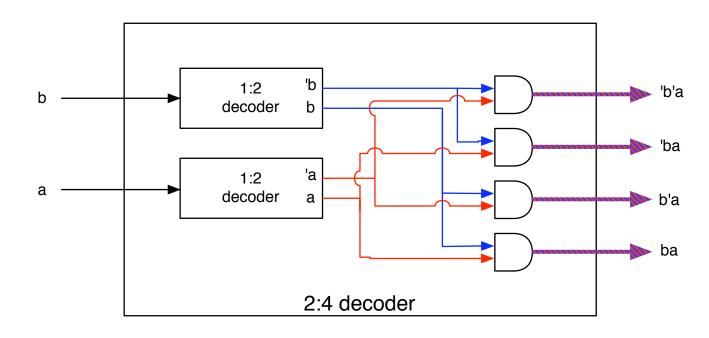

### **Decoders**

## Hierarchical design of decoder (2:4 decoder)

Takes n-bit input, uses it as an index to enable exactly one of  $2^n$  outputs

Figure: Source: Mano & Kime

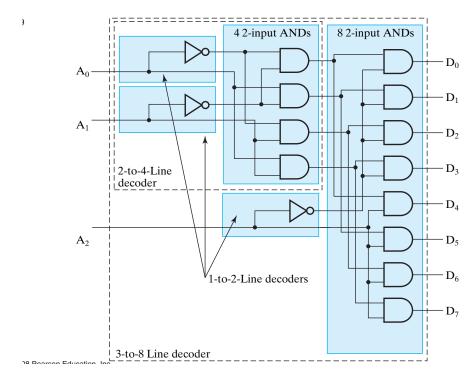

### Decoders

Takes n-bit input, uses it as an index to enable exactly one of  $2^n$  outputs

### Decoder (3:8)

#### Hierarchical design: use small decoders to build bigger decoder

Note: A<sub>2</sub> "selects" whether the 2-to-4 line decoder is active in th top half (A<sub>2</sub>=0) or the bottom (A<sub>2</sub>=1)

Figure: Source: Mano & Kime

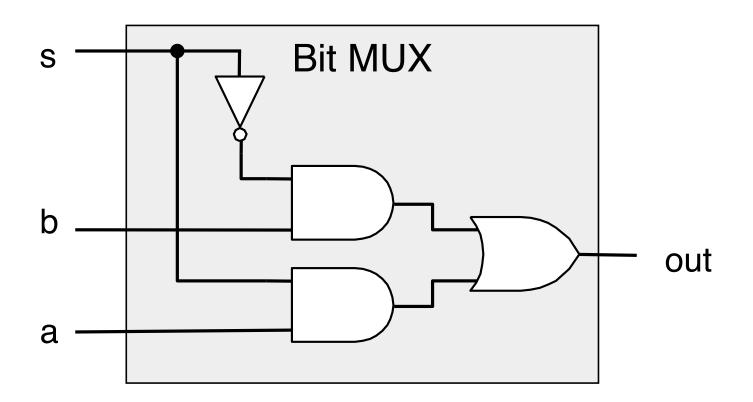

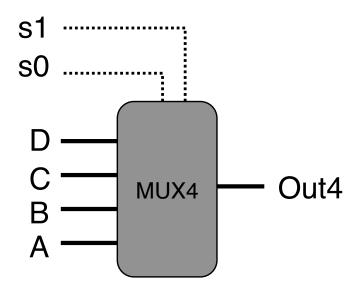

## Multiplexers

Using n-bit selector input, select among one of 2<sup>n</sup> choices

Figure: Source: CS:APP

## Multiplexers

Using n-bit selector input, select among one of 2<sup>n</sup> choices

Figure: Source: CS:APP

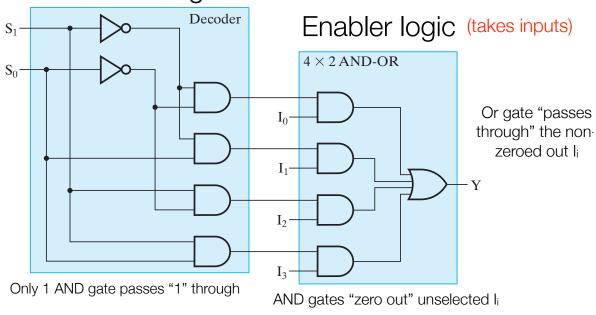

## Multiplexers

Using n-bit selector input, select among one of 2<sup>n</sup> choices

### Internal mux organization

3-26

#### Selector Logic (selects which input "flows through")

© 2008 Pearson Education, Inc.

M. Morris Mano & Charles R. Kime

LOGIC AND COMPUTER DESIGN FUNDAMENTALS. 4e

### Table of contents

Transistors: The building block of computers

### Combinational logic

Basic gates

More-than-2-input gates

#### Functional completeness

The set of logic gates {NOT, AND, OR} is universal The NAND gate is universal The NOR gate is universal

#### Combinational logic

Decoders Multiplexers

PA6 Demo code: directMapped read logic

directMapped read logic